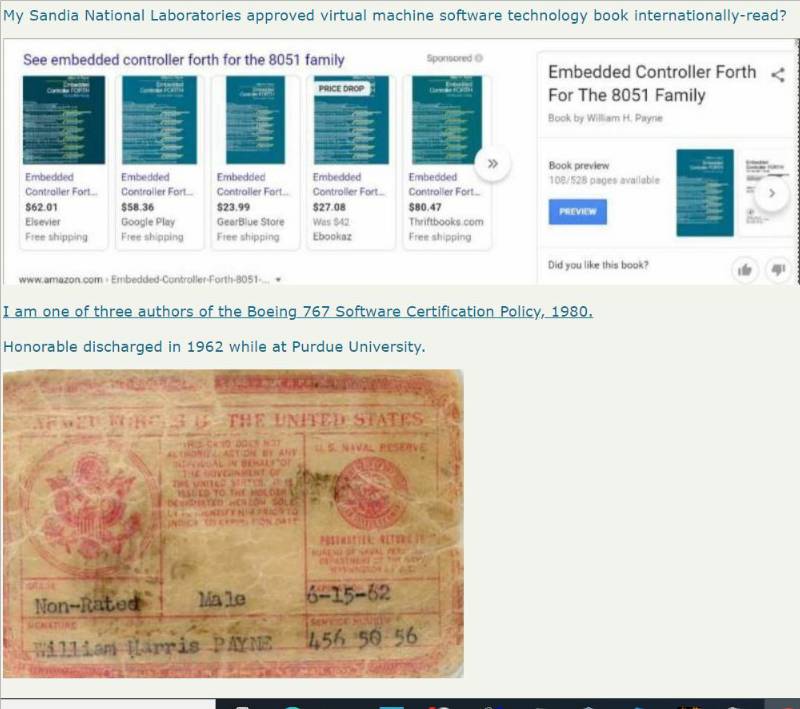

7/27/24 Conduct unbecoming navy officer Admiral William H Payne Complaint. 7/19/24

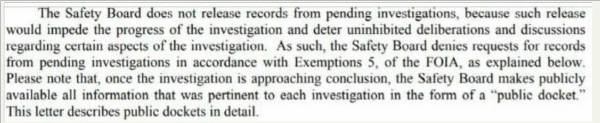

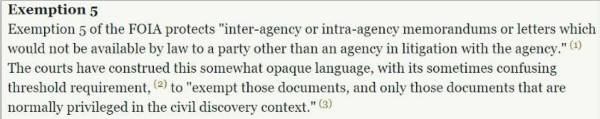

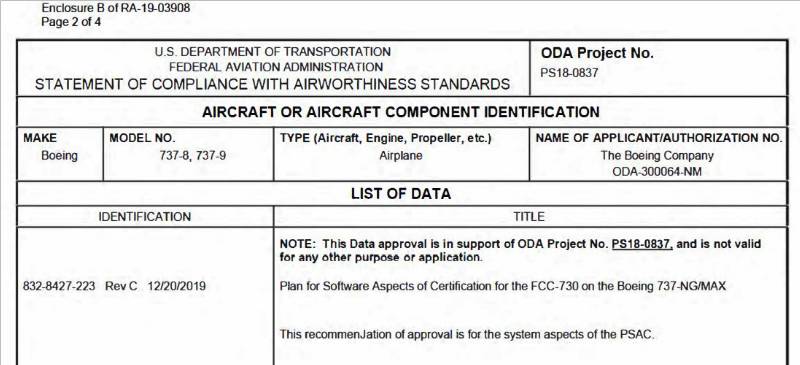

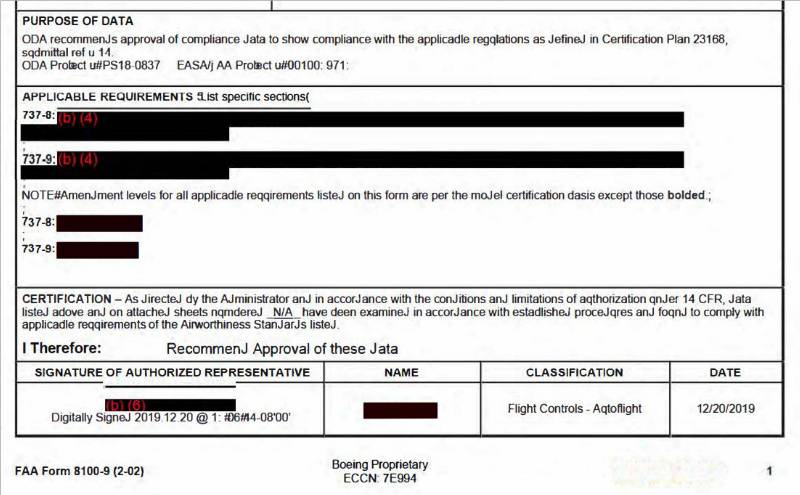

1/24/24. Kaneohe Poseiden P8A FOIA. 1/10/24. liaison 1. communication or cooperation which facilitates1/8/24. FOIA.GOV.12/2/23. policy. a course or principle of action adopted or proposed by a government, party, business, or individual. 11/25/23. bamboozle11/11/23. certification11/10/23. retaliation 11/9/23. nemesis11/7/23. con persuade (someone) to do or believe something, typically by use of a deception. 10/31/23 conned 7/5/23 Reprimand: "a rebuke, especially an official one.3/22/23. Phone numbers issues. 1-855-658-2676.3/21/23. Phone message from US government?.3/20/23 Feb 27, 2023. 4:41?PM (2 days ago) 3/1/23 F-18 Carrier break and landing!.12/25/22 ,

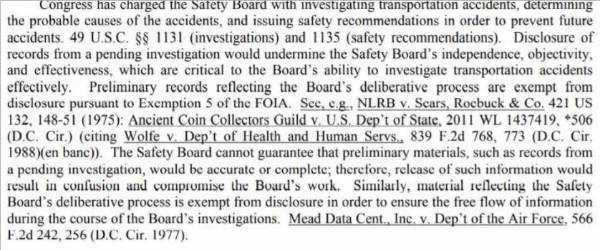

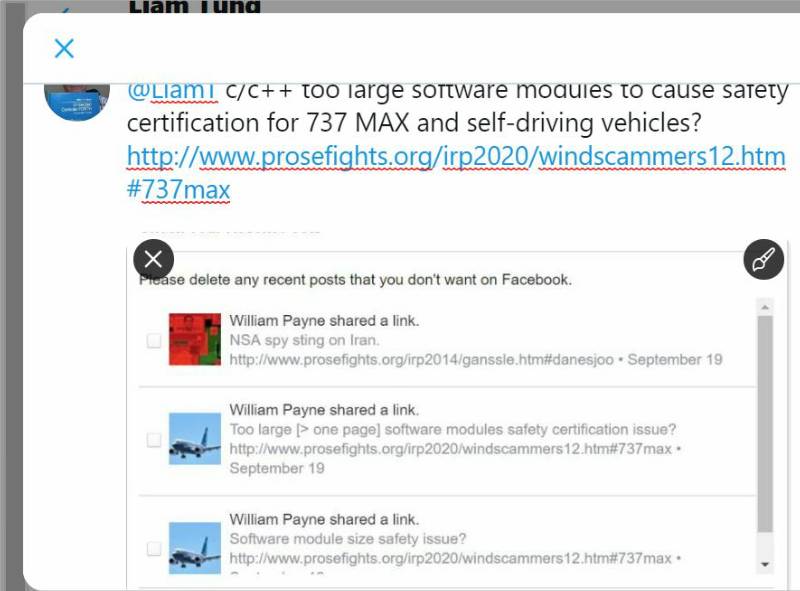

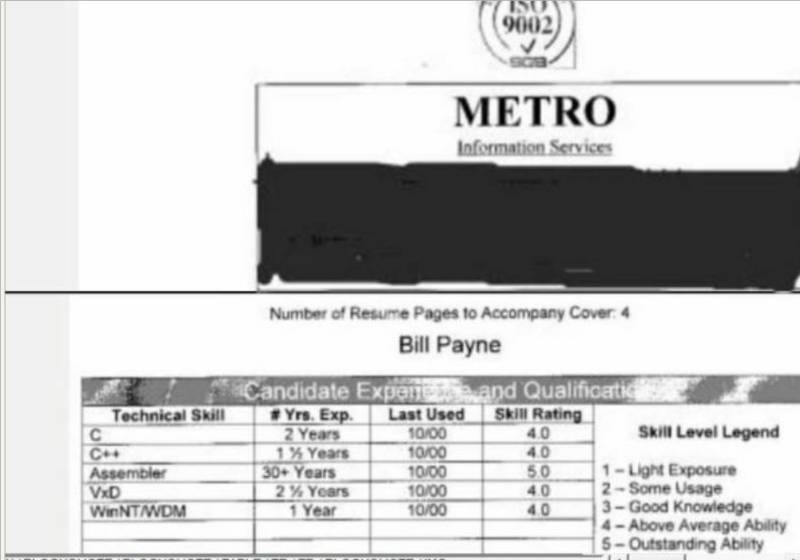

12/21/22. The statute of limitations for a FOIA claim is six years. However, a requester may refile their FOIA request to restart the statute of limitations.Feb 21, 201711/24/22. Airbus A220 autopilot warning. Full coverage.9/18/22 4/3/22 prosefights hacked. Again. :( Hacking attempted recovery 4.6.22. 2/5/22. __________________ 5/01/22. Linus Torvalds reveals the 'true' anniversary of Linux code.9/21/21. US Navy software FOIA request.9/3/21. Christopher Julka (703)-697-0031 DONFOIAPublicLiaison@navy.mil.8/24/21. c/c++ wind turbine software use too? NTSB 8/20/21 phone message.

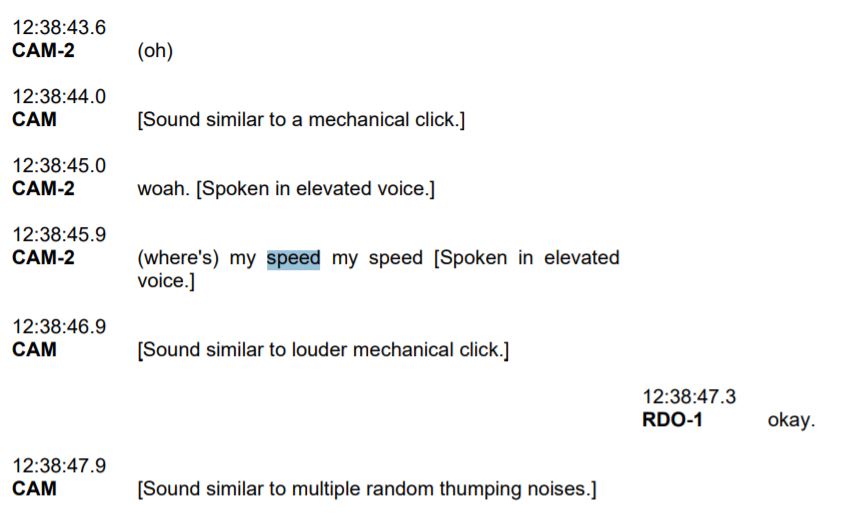

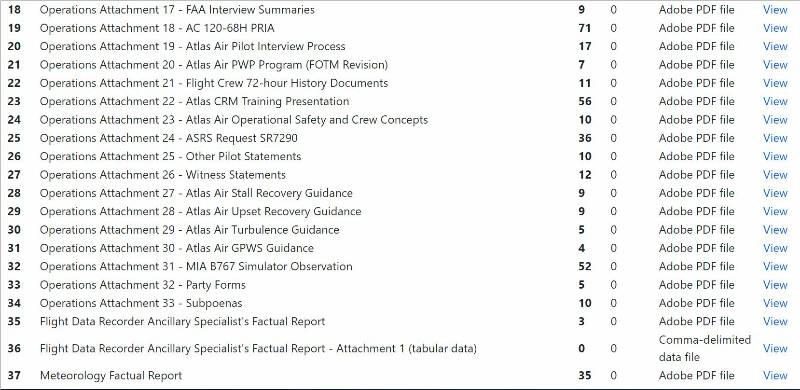

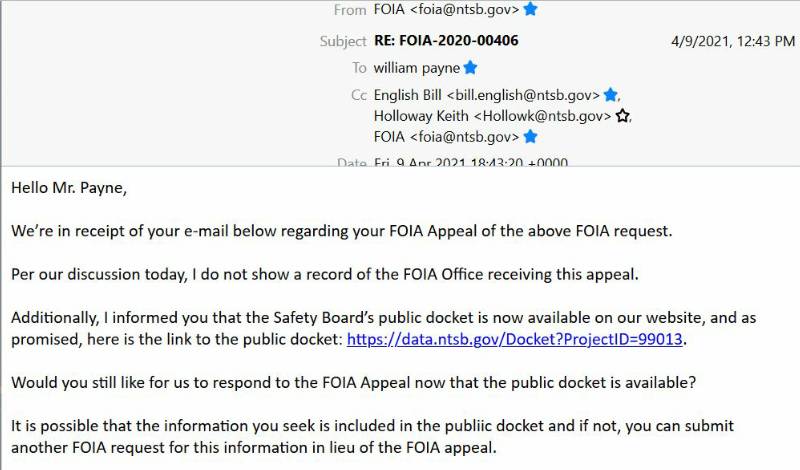

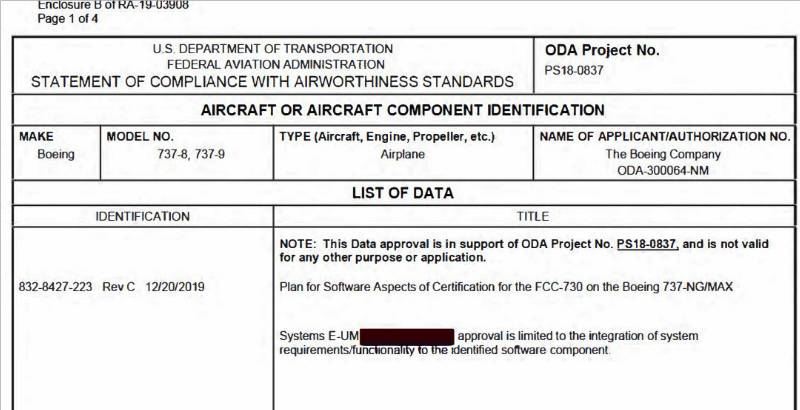

4/22/21. 4/21/21. Software tehnology? c/c++? Scary USS Gerald R. Ford - How Powerful is the CVN-78? US Navy's $13 Billion Aircraft Carrier.4/20/21. Speed display disappear? Software issue? "(where's) my speed my speed"4/18/21. 4/17/21. Where is air speed? 4/1921. 4/16/21. NTSB Ms Tamara Crawford phone conversation 4/16.4/1421. 4/13/21. 'view' oly appeared starting today? 4/12/21. What computers? How many modules? Lines of code for each module?4/11/21

4/19/21. 4/10/21.

3/23/21. LIGHTWEIGHT OS FOR ANY PLATFORM. 3/20/21. 3/22/21 Attachments.

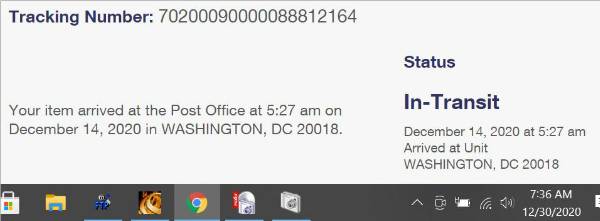

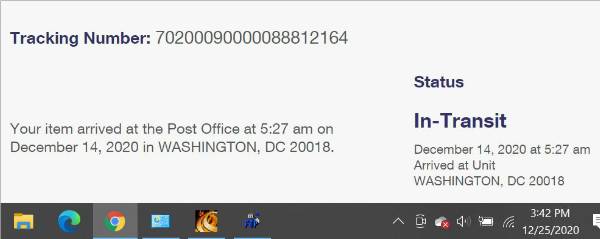

2/4/21. 12/30/20. 12/25/20. 12/22/20. :( !!!

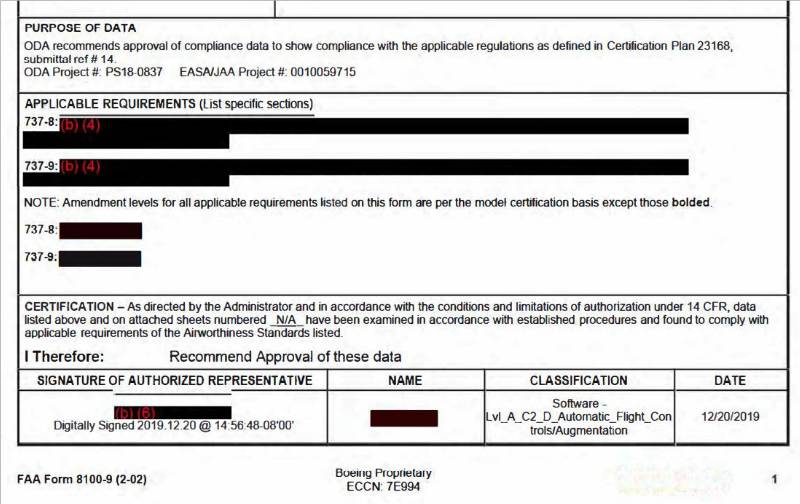

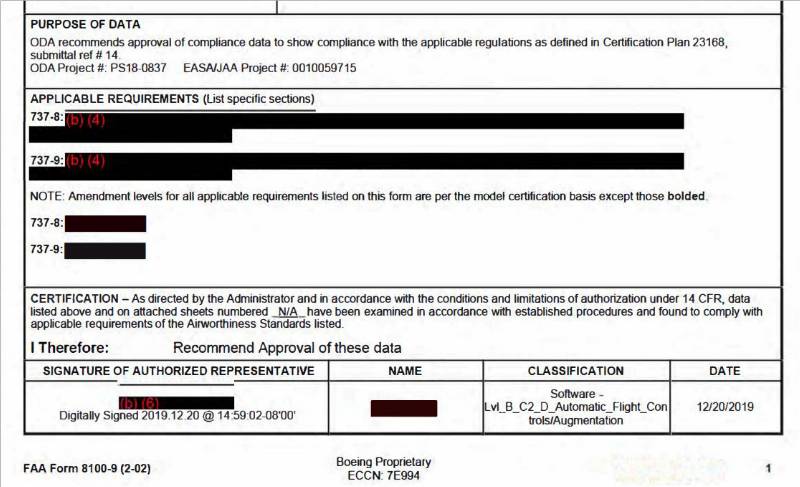

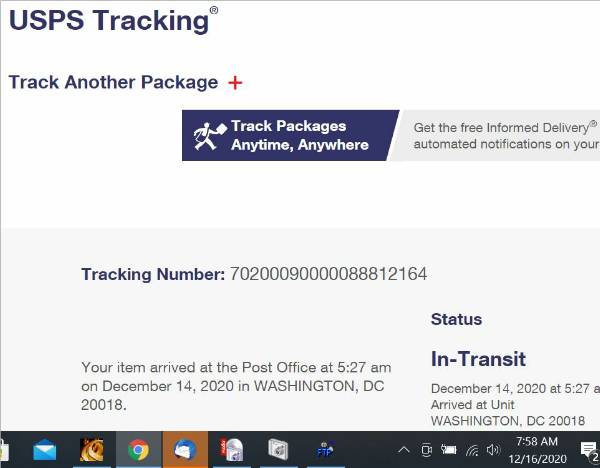

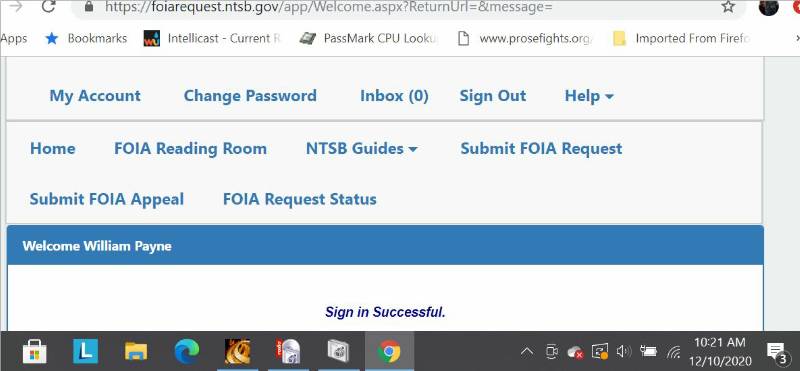

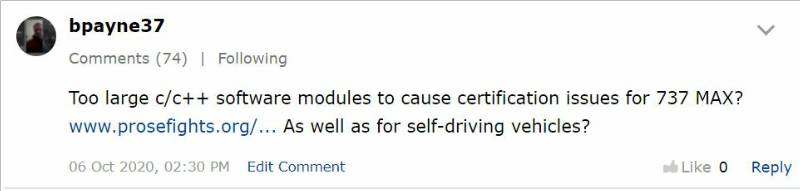

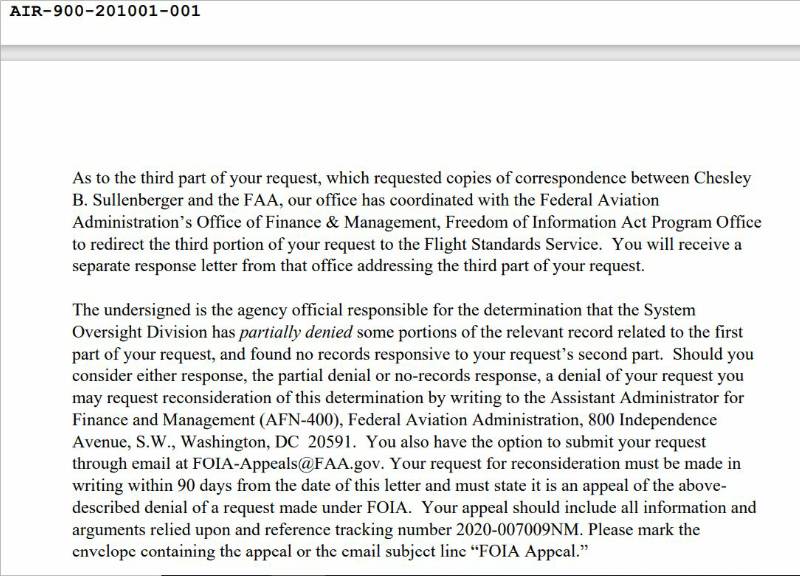

12/22/20. :( !! 12/21/20. :( ! 12/17/20. :( 12/16/20. Something wrong? 12/15/10 12/14/20. 12/10/20. 12/8/20. Tuesday December 8, 2020 14:43 10/26/20 FAA FOIA lawsuit - District of Columbia.. Boeing 787: A Financial Engineering Nightmare?.10/6/20. ____ 10/5/20. Liberal arts 'educated'? Linux 5 day course in focus because of 737 MAX and Raspberry Pi 4B.10/4/20 Programming languages: Java founder James Gosling reveals more on Java and Android.10/1/20.

9/18/20. Unable to shrink email.9/14/20 9/11/20 ntsb foia status message.8/11/20. ____ This surprise Linux malware warning shows that hackers are changing their targets. 8/10/20. FAA Dave Duff phone message 1 2. 8/01/20.8/7/20. Where is Mark House?

|

Another request?

Another request?

1

1 1

1

1

1 1

1